OpenTitan Partners Release First Open-Source Chip to Commercial Market

The latest hardware RoT chip is community-accessible, ensuring security (perhaps paradoxically) through transparency.

In a first for open-source hardware, the lowRISC Community Interest Company (CIC) and the OpenTitan Coalition have announced the first nonproprietary chip to reach the commercial market. Compared to proprietary hardware, open-source hardware allows more engineers to design and audit custom devices, expanding the resources and vision of a single project well beyond what is possible in a single organization.

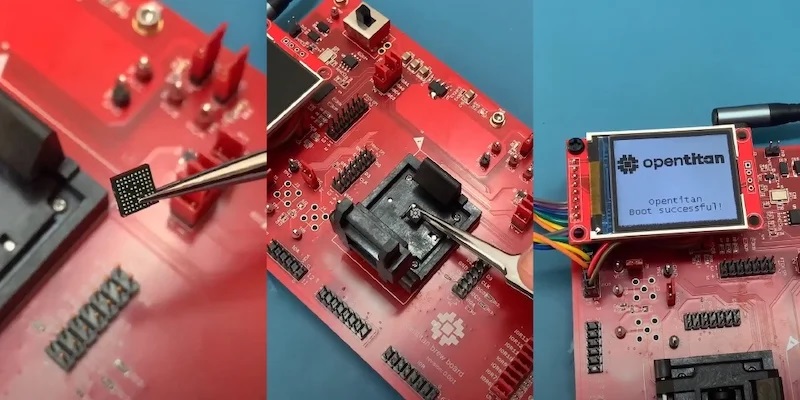

OpenTitan says its newest silicon is the first commercial-grade, open-source chip.

Nine partners spearheaded this project: Google, Winbond, Nuvoton, zeroRISC, Rivos, Western Digital, Seagate, ETH Zurich, and Giesecke+Devrien. Together, they set out to build a transparent and trustworthy security chip; now, the OpenTitan project is available on a commercial scale

Security Through Transparency

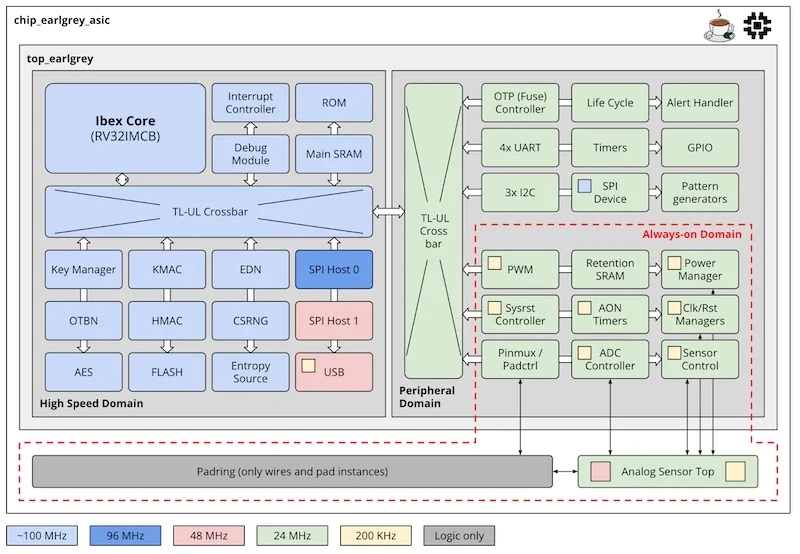

While the lowRISC CIC and the OpenTitan Coalition have not released all of the specs behind the new OpenTitan silicon, they have revealed that the chip is based on the previously taped-out Earl Grey discrete MCU. Digging into the datasheet, we see a RISC-V Ibex core at the heart of the chip, running at a 100-MHz clock speed with the open-source security features of the RISC-V architecture baked into the core.

The Earl Grey block diagram highlights the security features in the high-speed and peripheral domains.

Outside the CPU, a bevy of peripherals provides I/O functionality and hardware security through cryptographic functions and OTP handling. These are complemented by typical MCU bells and whistles, including GPIO, I2C, UART, SPI, and USB support, providing an all-in-one security solution in various applications.

Commercial Open-Source Hardware

Since 2019, the OpenTitan project has been developing an open-source silicon root of trust (RoT) chip to address security challenges. The first tapeout occurred in June 2023, and now a new discrete based on the Earl Grey design is available to the public.

OpenTitan IP is open to anyone, allowing designers to evaluate the IP in their own use cases and find security weaknesses.

While an open-source approach to hardware may seem counterintuitive, a nonproprietary strategy can be useful and effective. Openly accessible schematics and design files allows designers from all backgrounds to audit and test the RoT chips' performance. That way, if there is a weak point, the same designers can work together to solve the problem.

OpenTitan Continues Its Momentum

The group behind this OpenTitan silicon is now working toward the “Darjeeling” secure execution environment (SEE), along with the “Chai” SEE. The group also plans to release an updated Earl Grey discrete with performance improvements and development support. The collaborators believe its OpenTitan IP can benefit numerous applications, from motherboards to IoT devices, all thanks to its transparent, hardware-based security and community-driven effort.

.jpg)

.jpg)