Espressif Systems recently announced the upcoming release of the ESP32-S31, a dual-core system-on-chip (SoC) with integrated wireless and wired connectivity. The company positions this chip to address the increasing complexity of Internet of Things (IoT) hardware, which needs a balance of high-speed data transmission, low-power operation, and processing power.

The ESP32-S31. Image used courtesy of Espressif

By consolidating Wi-Fi 6, Bluetooth 5.4, and IEEE 802.15.4 onto a single silicon die, Espressif designed the ESP32-S31 to help engineers build complex devices such as smart speakers, industrial automation hubs, and voice-controlled appliances.

Key Features of the Multi-Protocol Chip

Espressif claims its ESP32-S31 helps engineers manage demanding workloads with its dual-core 32-bit RISC-V microcontroller, which operates at speeds up to 320 MHz. To support edge AI workloads, one core features a 128-bit-wide data path with SIMD instructions to accelerate parallel processing.

The chip also includes 512 KB of internal SRAM and provides connectivity for 250 MHz of 8-bit DDR PSRAM, with the option to expand external memory through multiple dedicated SPI interfaces that support high-speed Octal SPI mode.

From a connectivity standpoint, the SoC also has a built-in multi-protocol radio system. For example, it supports 2.4 GHz Wi-Fi 6 (802.11ax) as well as an IEEE 802.15.4 radio for Thread and Zigbee, enabling native Matter protocol support. In addition, the SoC offers Bluetooth 5.4 support with Low Energy (LE) for high-quality audio streaming via the LC3 codec, Bluetooth Mesh 1.1 for device-to-device communication, and Bluetooth Classic (BR/EDR) for legacy audio compatibility.

In addition to general-purpose computing, Espressif designed the ESP32-S31 to drive advanced human-machine interfaces (HMIs). To this end, the SoC contains a DVP camera interface and an LCD controller that supports parallel RGB, I8080, and MOTO6800 interfaces. To maintain high frame rates without taxing the main CPU, Espressif included dedicated hardware accelerators, including a JPEG codec, a Pixel Processing Accelerator (PPA), and a 2D-DMA engine.

SIMD Parallelism in Edge Microcontrollers

Single Instruction, Multiple Data (SIMD) is a computing architecture that allows a processor to perform the same operation on multiple data points simultaneously within a single clock cycle. In ordinary scalar processing, a CPU executes one instruction on one piece of data at a time. While this approach may be sufficient for general logic, it creates bottlenecks when processing large arrays of information, such as digitized audio signals or image pixel buffers. SIMD overcomes this by using wider registers, such as 64-, 128-, or 256-bit registers, which can be partitioned into smaller segments to hold multiple values.

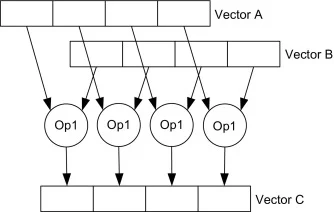

Example of a SIMD execution unit. Image used courtesy of Science Direct

When a SIMD instruction is executed, the hardware performs a mathematical or logical operation on all segments of the wide register simultaneously. For example, a 128-bit register can be treated as four 32-bit integers; a single SIMD add instruction would sum all four pairs of integers in the time it would take a standard processor to sum just one.

This parallel execution speeds up digital signal processing and machine learning tasks, such as Multiply-Accumulate (MAC) operations, which are the fundamental building blocks of neural networks. By reducing the number of cycles required to process data sets, SIMD hardware decreases the overall execution time and power consumption of the system, enabling complex algorithms to run on small, resource-constrained edge devices.

Facilitating Intelligent IoT Hardware

Espressif’s new chip is currently in sampling for select customers. Developers can access it through the company’s open-source IoT Development Framework (ESP-IDF), as well as specialized libraries like ESP-Matter, ESP-BLE-AUDIO, and the ESP Graphics Management Framework (ESP-GMF).