Recent updates show where RISC-V is heading, from compact ESP32 devices to one of the biggest names in mainstream computing.

RISC-V used to be something you’d only see if you were really into dev boards or ISA talks. Now, it’s appearing in real hardware and in the plans of major companies. This change is happening because teams want more control over their computing and more flexibility with software—and they don’t want to be stuck with just one option.

This roundup covers six updates for RISC-V: three are hands-on platforms using Espressif’s RISC-V chips, and three are bigger signs from the ecosystem. Together, they show RISC-V growing in two ways: as the backbone of many smaller connected devices and as the subject of keen interest among large semiconductor companies and governments alike.

Arduino Packs Wi-Fi 6, Thread, and LoRa Into a Pocket Controller

Arduino’s Nesso N1, developed in collaboration with M5Stack and based on the ESP32 C6, is designed to make prototyping feel easy and approachable—not just another bare-circuit board on your desk. It comes in a compact case, featuring a 1.14-inch IPS touchscreen, built-in sensors such as a six-axis IMU, and a full range of wireless connectivity options, including Wi-Fi 6, Bluetooth LE, and 802.15.4 for Thread or Zigbee.

The Nesso N1 uses a removable IPEX4 antenna to support sub-GHz LoRa operation without relying on an internal trace antenna. Image used courtesy of Arduino

If you need to connect over longer distances, the Nesso N1 includes a Semtech SX1262 LoRa transceiver, an RF front end, and a detachable IPEX4 antenna. The device also allocates memory across on-chip flash, SRAM, and a 16-MB external SPI flash. One thoughtful design detail: the ESP32 C6 uses separate chip select lines to share its SPI bus between the display controller and the LoRa transceiver, so you don’t have to worry about data traffic getting mixed up.

You can power the Nesso N1 with either USB-C or its built-in, 250-mAh Li-Po battery, which includes a fuel gauge to track charging. The board supplies both 3.3 V and a boosted 5-V rail for any external modules that may be added later. As for the software side of things, you can use the familiar Arduino IDE, MicroPython, or UIFlow. Users can also connect to Arduino Cloud for dashboards, logging, or remote monitoring.

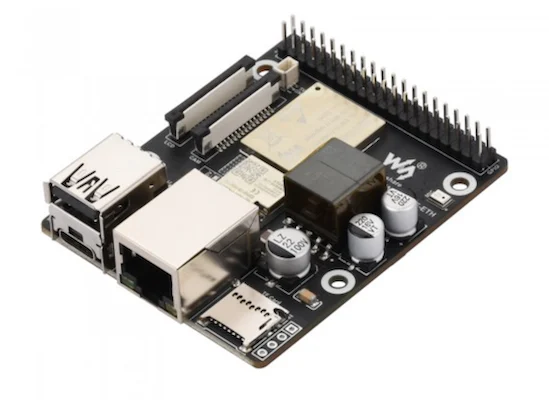

Waveshare Couples Compute With Wi-Fi 6, Ethernet, and PoE

Waveshare’s ESP32 P4 Wi-Fi 6 POE ETH board currently uses two processors. The ESP32 P4 is the main controller, while an ESP32 C6 module manages Wi-Fi 6 and Bluetooth LE through an SDIO connection. The P4 is designed for multimedia and interface-heavy projects, as well as basic sensor tasks.

Waveshare’s design pairs multimedia-focused processing with integrated networking, using separate ESP32-P4 and ESP32-C6 devices to split application and connectivity workloads. Image used courtesy of Waveshare

The ESP32 P4 features a dual-core RISC-V CPU running at about 360 MHz. It supports up to 32 MB of PSRAM and includes components like MIPI CSI and DSI, an image signal processor, JPEG hardware, pixel acceleration, and an H.264 encoder. Waveshare also provides 100-Mbps Ethernet with an IP101 PHY and a header for an optional PoE module, so you can use one cable for both power and networking.

The board also includes microSD storage, both Type A and Type C USB ports, I2C and UART headers, built-in audio hardware, and two 40-pin headers for GPIOs and common interfaces. This platform is a good choice if your project needs a camera, screen, and audio, and you want to avoid building everything from the ground up.

Lilygo Turns the ESP32 P4 Into a Handheld HMI

While the Waveshare board feels more like a bench platform, Lilygo designed the T Display P4 as a portable device. This compact handheld device combines an ESP32 P4 with an ESP32 C6, measuring approximately 63 mm x 109 mm x 22 mm, and features a large screen, camera support, and multiple wireless capabilities.

There are two display options available. One includes a 4.1-inch AMOLED capacitive touchscreen with a resolution of 568 x 1232 pixels and a rear-mounted 2-MP OV2710 MIPI camera. The other features a 4.05-inch TFT display with a resolution of 540 x 1168 pixels and a punch-hole design for the front-facing camera. Both variants can maintain the same functionality, with the P4 handling the intensive user interface and media tasks, while the C6 manages Wi-Fi 6 and Bluetooth LE connectivity.

A handheld ESP32-P4 device that combines a large touchscreen, camera support, and Wi-Fi 6, LoRa, and GNSS in one portable unit. Image used courtesy of Lilygo

Radio-wise, it goes beyond Wi-Fi and Bluetooth, adding an SX1262 LoRa transceiver with regional options and up to +22-dBm transmit power, plus an L76K GNSS receiver. The Lilygo T Display P4 also includes a variety of features, including Ethernet, a 9-axis IMU, an audio codec and amplifier driving an onboard speaker, microSD expansion, haptic feedback via a vibration motor, RTC support, and battery charging over USB.

India’s Push for an Indigenous, Scalable Processor Pipeline

DHRUV64 is India’s first homegrown 1.0-GHz, 64-bit dual-core microprocessor, developed by C-DAC through the Microprocessor Development Programme. C-DAC's main goal was to create a local processor platform, so users wouldn't need to rely on imported microprocessors for every need.

Developed under the Digital India RISC-V initiative, DHRUV64 is intended to anchor a scalable, open processor platform for academia, startups, and industry. Image used courtesy of pib.gov

DHRUV64 is not a standalone initiative; rather, it is part of a broader effort associated with the Digital India RISC-V program, which aims to develop processors based on an open architecture. This strategy effectively minimizes licensing constraints, thereby promoting resource sharing across academia, startups, and industry. It aligns with C-DAC's broader strategic vision to develop the Dhanush and Dhanush Plus processors, which are engineered to boost performance and expand application versatility.

Qualcomm Acquires Ventana to Deepen RISC-V Engineering

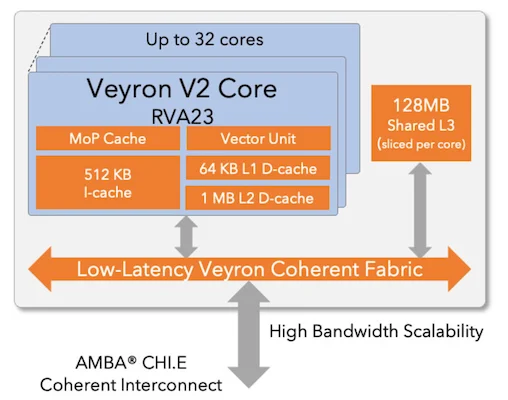

Qualcomm recently acquired Ventana Micro Systems to bolster its RISC-V capabilities within the CPU division. Ventana is well known for its advanced RISC-V architectures and has made significant contributions to the RISC-V ecosystem. This strategic move allows Qualcomm to deepen its expertise and leverage Ventana's innovative solutions in the rapidly evolving landscape of open-source processor architectures. Qualcomm has stated that this deal will particularly strengthen its custom Oryon technology.

Diagram of Veyron V2, Ventana’s second-generation high-performance RISC-V CPU. Image used courtesy of Ventana Micro Systems

The key takeaway is that Qualcomm is not treating RISC-V as merely a small controller side project. By investing significant resources in deepening its RISC-V ISA capabilities, Qualcomm indicates it expects RISC-V to play an important role in its future CPU plans, particularly as the demands of AI-driven workloads will continue to increase CPU design requirements over the next few years.

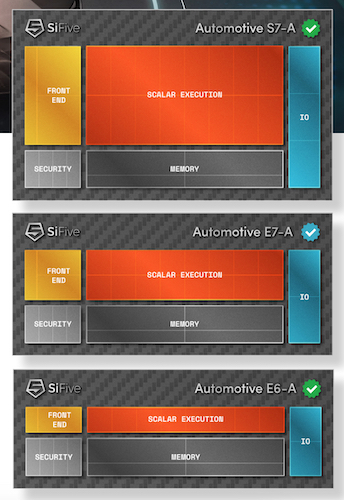

Quintauris and SiFive Align on Reference Architectures for Automotive Systems

Quintauris and SiFive are collaborating to address a prevalent challenge in the automotive sector: integration difficulties. This partnership is designed to ensure that SiFive's intellectual property (IP) operates seamlessly within Quintauris' reference architectures, while paying particular attention to automotive zonal systems, advanced driver-assistance systems (ADAS), and electronic control units (ECUs). In this context, achieving consistency and compatibility is just as crucial as meeting raw performance goals or the costs associated with mismatched toolchains.

SiFive's automotive RISC-V processors. Image used courtesy of SiFive

Quintauris focuses on developing profiles, reference architectures, and software components that help the RISC-V architecture scale across various industries. By integrating SiFive’s processor IP into this framework, the two companies aim to provide developers with a more standardized foundation for their projects, ultimately reducing unexpected challenges when transitioning from prototype to production.

RISC-V Goes Big

The compilation of these six updates indicates that RISC-V is transitioning from niche applications to tangible products and long-term strategies. At one end of the spectrum, ESP32-based platforms are now being shipped with integrated displays, radios, sensors, and power options, thereby enhancing their utility beyond mere demonstrations. On the opposite end, national initiatives, acquisitions, and industry collaborations are establishing the foundational elements necessary for the practical implementation of RISC-V at scale. RISC-V is increasingly perceived not merely as an "interesting alternative" but as a viable framework around which teams are strategically planning.