Developed with SiFive, the dual-core SoC uses patented error correction to achieve a record 16.8 µW/MHz/DMIPS, targeting next-gen wearables, drones, and IoT sensors.

In a move aimed at the growing market for intelligent edge devices, Upbeat Technology announced today its new UP201/UP301 family of microcontrollers (MCUs). Developed in collaboration with SiFive, the new SoC integrates a dual-core RISC-V architecture with custom AI accelerators and advanced power-saving features.

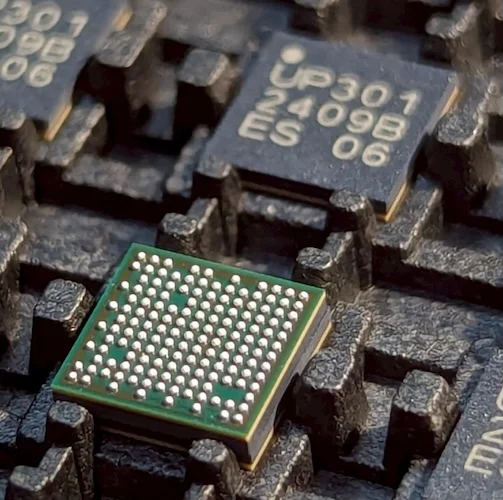

The UP301 MCU includes RISC-V CPUs and AI accelerators. Image used courtesy of Upbeat Technology

In advance of Upbeat’s technology presentation at the RISC-V Summit, All About Circuits spoke with Upbeat Technology President and CEO, Jerry Chen.

Big Dreams

Jerry Chen began his career at Intel, working on the development of the Itanium processor. He later spent time at Apple and Inphi. Along the way, he learned that “we need to be audacious and dream big.” Those big dreams led to the founding of Upbeat Technology.

According to Chen, they raised between $6M and $7M to start the company in 2021. Their first major product was a low-power MEMS bone conducted microphone for wireless earbuds and smart eyeglasses.

Since then, they have increased funding to roughly $20M and are now announcing their second major technology innovation: a family of ultra-low power MCUs.

Near-Threshold Computing and EDAC: The Core Technology

The key feature of the UP201/UP301 MCU family is its aggressive power-saving strategy, built on two core patented technologies.

First, the chips employ Near-Threshold Conduction (NTC), allowing the digital logic to operate at voltages as low as 0.4V. This is significant because power consumption scales with the square of the voltage (P∝V2), yielding substantial energy savings.

Operating at such low voltages introduces timing challenges, including potential setup time violations. Upbeat addresses these with a second key innovation: a proprietary Error Detection and Correction (EDAC) architecture. This system, which includes a patented special flip-flop design, can catch and correct setup time violations that may occur at near-threshold voltages. This allows for reliable operation without sacrificing efficiency gains.

RISC-V for Superior Performance Over ARM

“For an application like a smartphone, there is a huge ARM ecosystem,” acknowledged Chen. However, for embedded applications where companies are building their own software anyway, switching to RISC-V allows better performance. As an example, Chen described that “Western Digital is a great supporter of RISC-V because it provides superior performance for their hard drive and SSD controllers.”

Combining the RISC-V architecture with NTC technology, Upbeat Technology claims that it can achieve approximately 40% lower power consumption than competing ARM solutions, based on Coremark benchmarks. The chip also supports dynamic frequency scaling to further optimize the power-to-performance ratio.

The UP201 and UP301 share the same ultra-low-power RISC-V CPUs and AI accelerators. The smaller UP201 is an AI SoC built for space-constrained applications that demand extreme battery life. The larger UP301 is an AI processor that supports higher-level vision applications and includes a richer set of peripheral interfaces.

Early Adopters: From Drones to AI Toys

The UP201/UP301 family is already being designed into several novel applications. One key client is developing a drone controller using the UP301, a project that aligns with efforts to build a drone ecosystem that is not reliant on Chinese technology.

Other early applications include AI-powered toys. The UP301 is paired with MEMS vibration sensors to enable low-power swipe and touch controls—for instance, making a toy giggle when "tickled". According to Chen, the combination of Upbeat's sensor technology and low-power AI processing allows them to “provide more innovation and create value for their customers.”

RISC-V Summit Demonstrations

If you will be attending the 2025 RISC-V Summit and want to learn more, Upbeat Technology will be presenting its products in the SiFive booth. Upbeat leaders will also give a presentation on ‘A Heterogeneous Dual-Core RISC-V Edge AI Platform for Power-Efficient Machine Learning’ on October 22, 2025, at 11:10 AM. It will feature live demos and hands-on training.

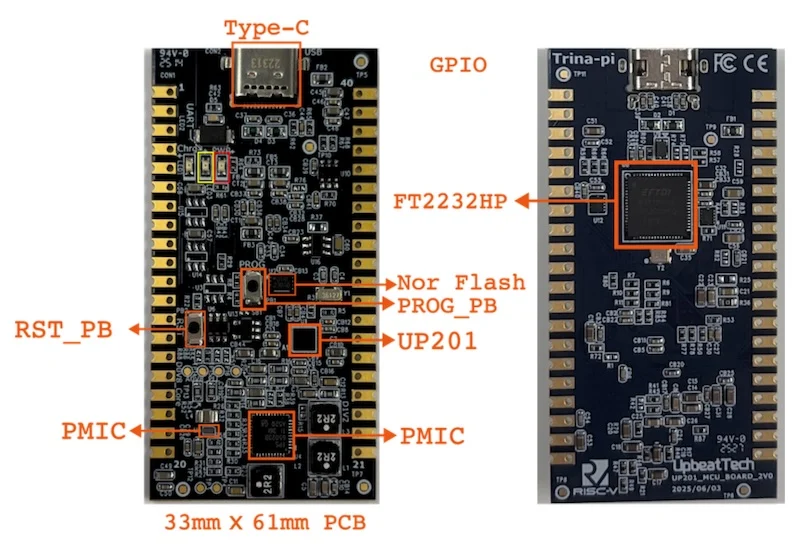

The Trina-Pi evaluation boards for the UP201/UP301 MCU family. Image used courtesy of Upbeat Technology

Chen explained that they are bringing Trina-PI eval boards to allow attendees to create a keyword spotting demonstration. With a microphone connected to the board, the system can wake and recognize 10 voice commands.

To assist engineers beginning development, the Trina-Pi evaluation board is slated for release this month, coinciding with the RISC-V Summit. The ICs themselves will be available in December 2025. A full SDK will be available for download on GitHub, providing a familiar access point for the developer community.

Featured image background used courtesy of Adobe Stock.