Semidynamics and Signature IP Expand Multi-Core RISC-V and CHI Options

Two relatively new players in the CPU world, Semidynamics and Signature IP, have announced multi-core RISC-V and CHI interconnect IP for compute-intensive applications like AI/ML.

As some experts predict the end of Moore’s law, the artificial intelligence and machine learning (AL/ML) industry needs to find ways to greatly increase computing power density and efficiency. Such gains call for monolithic multi-core and chiplet architectures and improved interconnects.

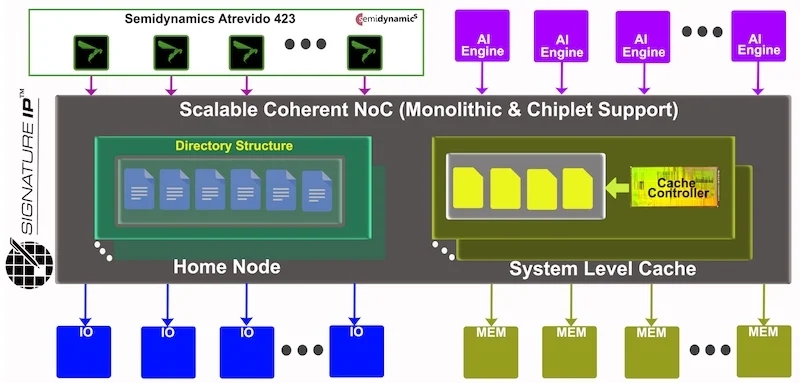

One of the newest announcements in the multi-core arena comes from a partnership between Semidynamics and Signature IP. The two intellectual property (IP) companies have created and tested a RISC-V multi-core environment and Coherent Hub Interface (CHI) interconnect for system-on-chip (SoC) developers.

Combined Semidynamics and Signature IP offering.

Semidynamics is a recent entrant to the RISC-V core creation market, while Signature IP is a newcomer to the network-on-chip (NoC) field.

Multiple Cores: The Key to AI and ML

Artificial intelligence, both generative and interpretive, and machine learning involve massively parallel mathematical operations, such as matrix multiplication. AI-related disciplines break down problems, comparisons, and calculations and compute those pieces in parallel. The smaller the pieces, the faster and more accurate the calculations will be.

Unfortunately, adding more discrete processors draws extra electrical power. In addition, the distance between the processors adds time to the process. The best current methodology to mitigate both of these issues is to put multiple cores in the same silicon or to place chiplets onto the same component substrate.

Signature IP's Advanced NoC Capabilities

While a multi-core architecture is a critical requirement for AI, without an efficient interconnect between cores, much of the cores’ processing power could go to waste. That’s where Signature IP comes in. The company's coherent network on chip (C-NoC) is directory-based with home-node support and can support both coherent and non-coherent traffic. It can also improve performance with optional system-level caches. Signature IP has an EDA development toolset with automation and operates under a simple licensing model.

.jpg)

Signature IP Coherent NoC (C-NoC).

Coherency enables higher performance in complex multi-core processors. When processors complete tasks unevenly, coherent (logically consistent) cache data give different cores access out of order. In general, different cores should not see different values for shared data. However, there are circumstances when non-coherence—different data in different caches—is required. The Signature IP CHI manages both coherent and non-coherent caches, minimizing lost clock cycles or collision errors.

Semidynamics Brings RISC-V to the Multi-Core Field

Most high-end, multi-core systems today use Intel, AMD, or Arm processing cores. Semidynamics is entering the mix with its newly available RISC-V cores. Semidynamics offers two customizable 64-bit RISC-V cores optimized for AI, ML, and other high-transaction requirements. The company refers to its customizability as an “open core surgery” approach. This lends the implementer greater hardware design flexibility and allows them to prototype and test the custom architecture on an FPGA to reduce test and verification time.

RISC-V began at the University of California at Berkeley in 2010 as a student research project on parallel computing. Over the intervening years, the open-source architecture slowly gained a following as an alternative to the commercially licensed Arm RISC IP. This allows companies like Semidynamics to develop RISC CPU designs that follow the RISC-V instruction set architecture (ISA) standard without license fees. Chip developers have a lot of freedom in their hardware design but can maintain industry compatibility by adhering to the open-source ISA.

RISC-V Joins the High-End CPU Market

Just a few years ago, virtually all high-performance CPUs came from Intel or AMD and were based on Intel’s x86 roots. Arm has become a serious player and, with its recent IPO, seems to be set for a solid future. Graphics processing units (GPUs) and tensor processing units (TPUs) are filling the processing space in AI server farms.

With RISC-V coming of age, offerings like the above from Semidynamics and Signature IP are poised to become a long-term fixture in the high-performance parallel computing world.

.jpg)

.jpg)